处理器与主存储器的物理连接与信号交互是计算机执行指令的基础。

物理总线结构

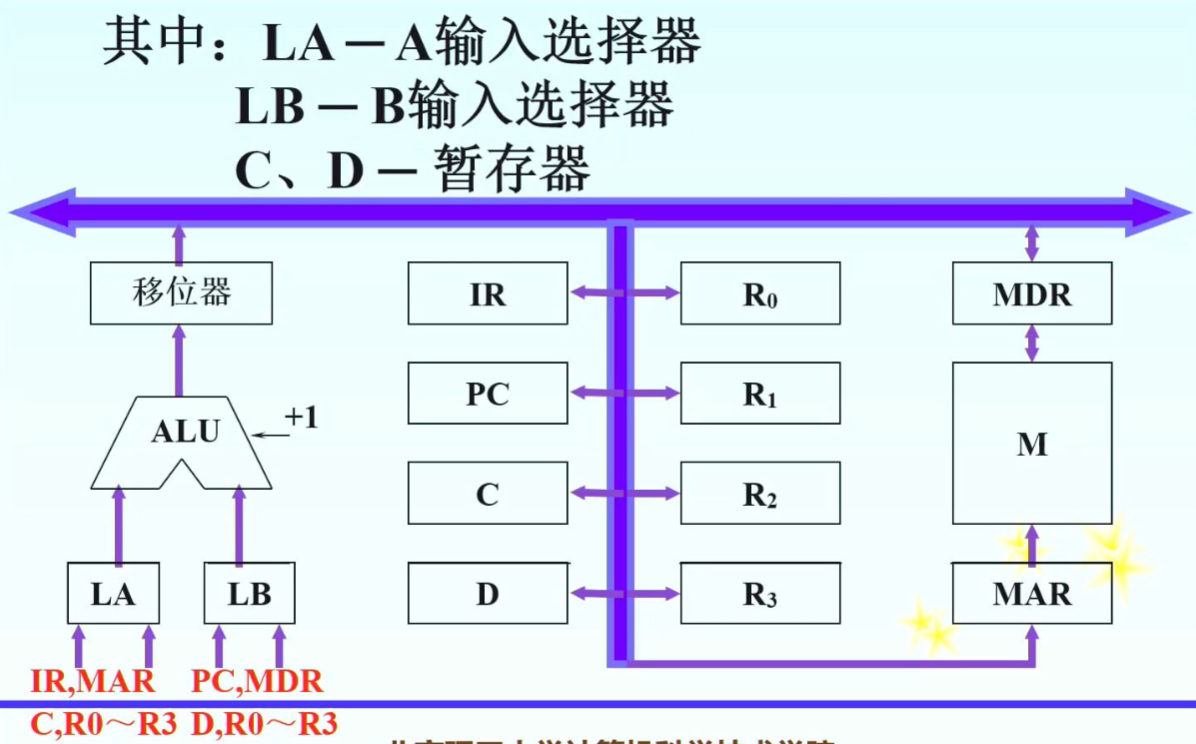

- 地址总线 (Address Bus): 单向,由 CPU 发出地址信号送往存储器。由 MAR 驱动。

- 数据总线 (Data Bus): 双向,承载 CPU 与主存之间的数据交换。连接到 MDR。

- 控制总线 (Control Bus):

交互逻辑与时序

性能匹配问题 重点

- 现状: 尽管内存技术(如 DDR1-DDR5)在不断演进,但“高速 CPU 与低速主存”的速度差异依然显著。

- 影响: 存储器的响应速度成为了制约计算机性能的瓶颈。

- 对策: 引入 Cache (高速缓存),利用其与 CPU 寄存器相同的制造工艺(速度匹配)来弥补主存的慢速,实现速度上的缓冲。