在现代计算机体系结构中,处理器(Processor)通常指封装在一起的多个 处理器内核 的集合。

核心参数

- 主频 (内部工作频率): 描述 CPU 内部数字脉冲信号震荡的速度。 重点

- 外频 (外部工作频率): 主板总线提供给 CPU 的基准时钟频率,用于同步 CPU 与内存等部件的通讯。

- 倍频系数:

- 公式: 。

- 历史背景: 早期内外频相等,随工艺发展 CPU 内部速度远超外部部件,故引入倍频技术。超频通常通过调整倍频或外频实现。

性能演进

- 单核时代: 主要依靠提高石英振荡器频率(主频)来提升性能。

- 多核时代: 当主频达到物理极限后,通过在一个封装内集成多个 内核 实现并行计算。

- 组成结构:

- 物理实现:

- 晶粒 (Die):处理器核心的物理载体。

- 访存接口部件:

- 扩展性:通过特定的接口,多个处理器可以进一步组成多路系统,提供更高的算力。

控制器

控制器是 CPU 的神经中枢,其核心本质是实现了 人类设计的指令到电子设备动作的最后转换。 重点 控制器功能与组成

微程序控制器

微程序控制器将指令的执行转化为一系列微指令的有序执行。

核心内容

微指令设计

指向原始笔记的链接

流水线

流水线技术

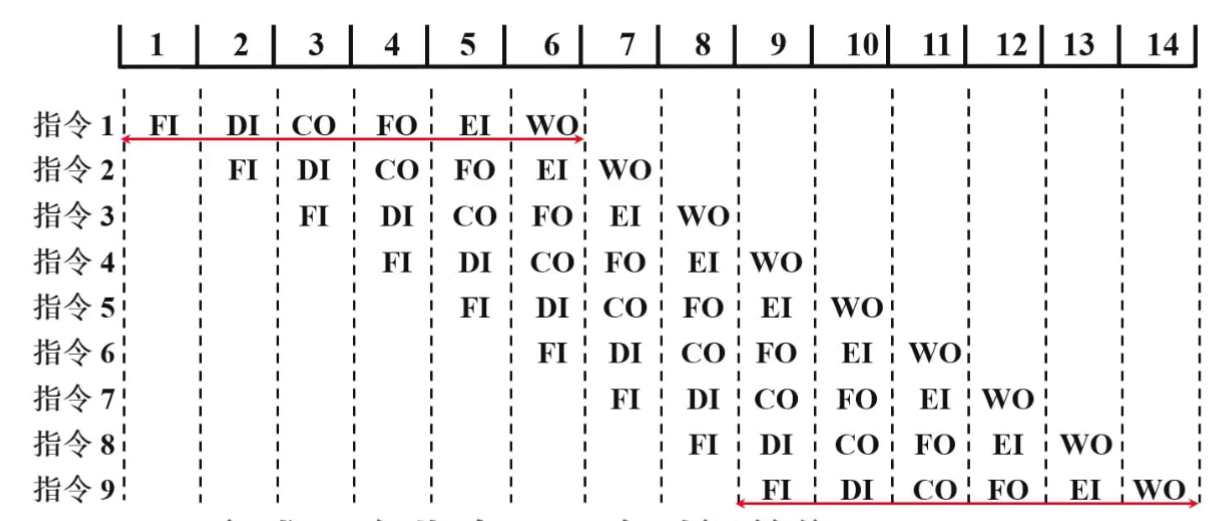

流水线技术通过重叠执行多条指令,显著提高 CPU 的执行速度和效率。

核心原理

- 子过程划分: 将指令执行过程分解为若干个子过程(如:取指 IF、译码 ID、计算地址 EX、取数 MEM、执行 WR)。

- 并行性: 不同的子过程由独立的硬件部件同时完成,使多条指令在空间上错开、时间上重叠。 重点

性能指标计算 重点

假设流水线为 段,每段执行时间均为 ,执行 条指令:

总执行时间 ():

- 解释:第一条指令跑完需 ,后续 条指令每隔 产出一个结果。

吞吐率 ():

- 最大吞吐率 (): 当 时,。

加速比 ():

效率 ():

- 。在时空图上体现为: 个任务占用的面积 / 个部件总面积。

- 。

流水线冲突 (相关性) 重点

- 结构相关 (资源冲突): 多条指令同时争用同一硬件资源(如同时访存)。

- 数据相关: 下一条指令依赖前一条指令的计算结果。

- 控制相关: 遇到转移指令(if, jump),导致流水线无法预知下一条指令的地址,产生“死区”。

流水线分类

- 静态流水线:

- 在同一时间内,流水线只能按一种功能连接工作(例如:一段时间内全做浮点加法,另一段时间全做定点乘法)。

- 排空 (Draining): 当从一种功能切换到另一种功能时,必须先等流水线中原有的任务全部流出(排空),并进行重新配置(设置初始条件),才能开始新功能的执行。这会带来额外的时间开销。

- 动态流水线:

- 允许在同一时间内,不同的功能段连接形成不同的功能子集,同时执行不同性质的操作(如浮点加法和定点乘法同时在流水线中运行)。

- 以此为基础,要求各功能段所使用的硬件资源彼此不冲突。

典型结构示例

课程中以一个 6 级流水线 为例描述指令执行过程:

- 取指 (IF)

- 译码 (ID)

- 计算操作数地址

- 取操作数

- 执行指令 (EX)

- 写回 (WB)

每个子过程由独立的硬件部件完成。若有 9 条指令在 6 级流水线上执行,理想情况下只需 个时间单位(相比串行的 个单位)。

指向原始笔记的链接